- A+

555定时器芯片由于使用方便灵活,应用非常广泛。常用在波形的产生与变化、测量与控制等许多领域。家用电器、电子玩具中都很常见,是非常经典的一款芯片。

究竟有多经典,甚至可以出它的手办模型。

由于广受市场欢迎,许多芯片公司都各自推出了555定时器芯片。尽管产品型号繁多,芯片内部电路的实现不尽相同,但他们最终实现的功能和外部引脚的排列完全相同。

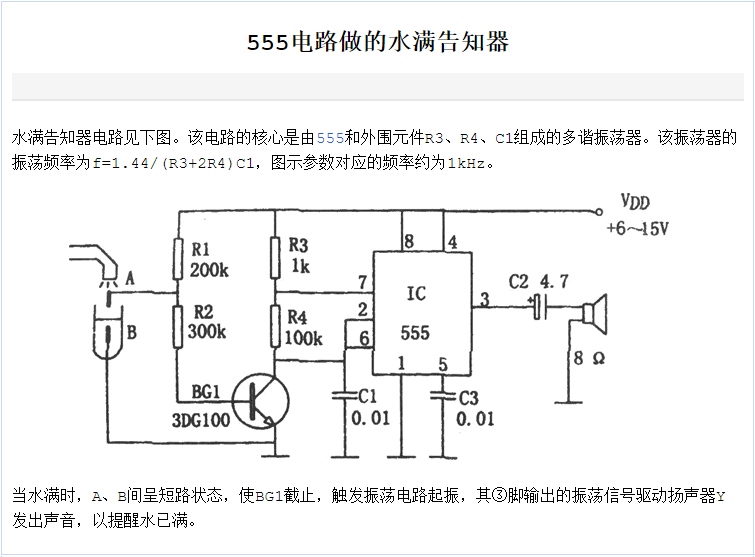

网上有很多555定时器做的应用电路,但是讲解都非常粗陋简略,可读性很差,比如这样的文章:

下面就以其中一款555定时器芯片为例,分析芯片的内部电路,讲解其工作原理。只要了解了芯片的工作原理,看各种芯片的应用电路时就会得心应手。

目录:

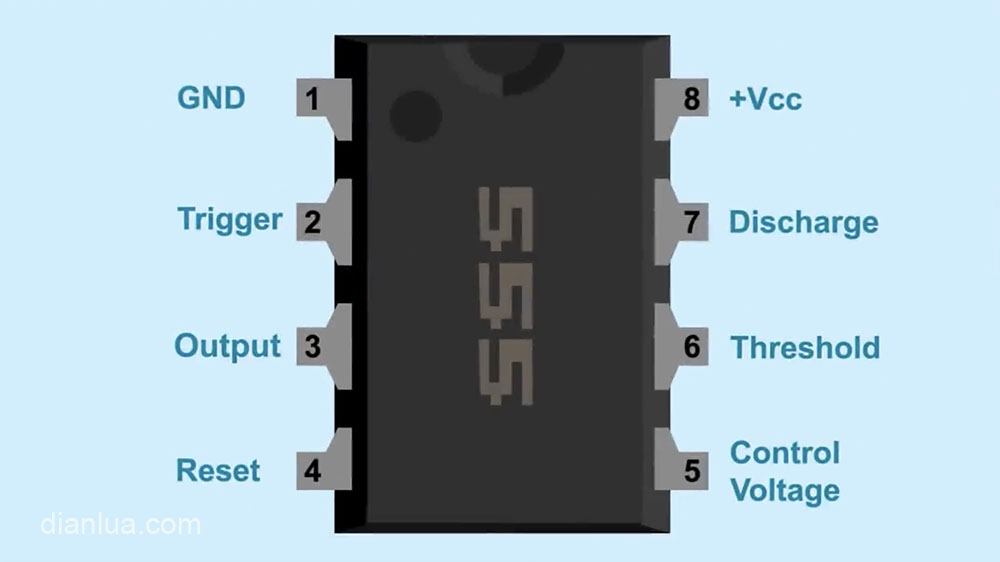

一、芯片引脚定义

二、芯片内部结构

三、等效图组成说明

四、等效图各功能区分析:分压电路 + 电压比较器

五、等效图各功能区分析:RS触发器

六、等效图各功能区分析:电压比较器 + RS触发器

七、等效图各功能区分析:555定时器芯片的PIN5(第5脚)

八、等效图各功能区分析:555定时器芯片的PIN3(第3脚)

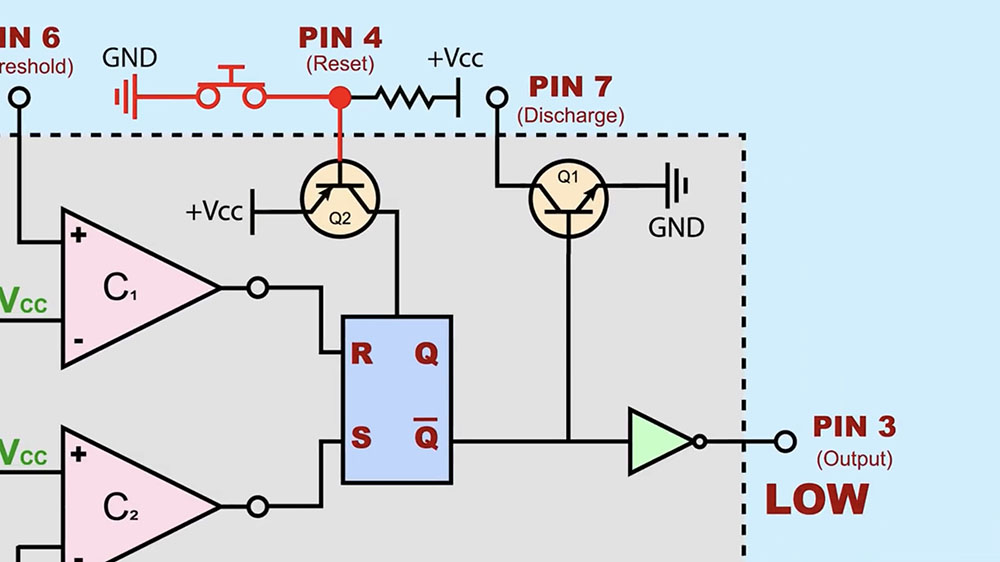

九、等效图各功能区分析:555定时器芯片的PIN4(第4脚)、PIN7(第7脚)

十、最后

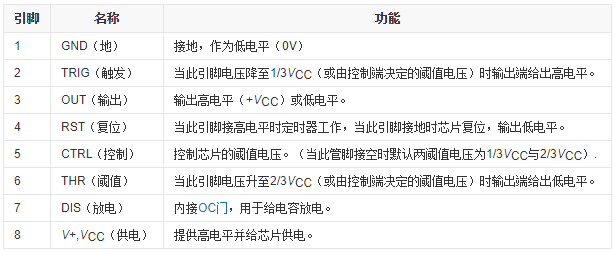

555定时器有8个脚,各脚定义如下。

各脚的详细定义见下表。(英文名称均为缩写)

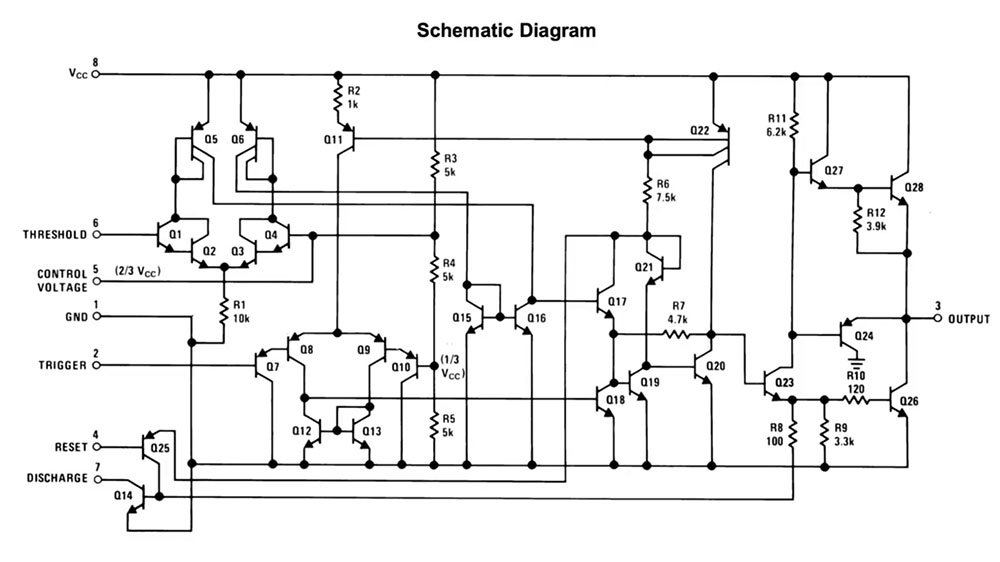

打开555定时器的数据手册,可以看到芯片的内部电路。

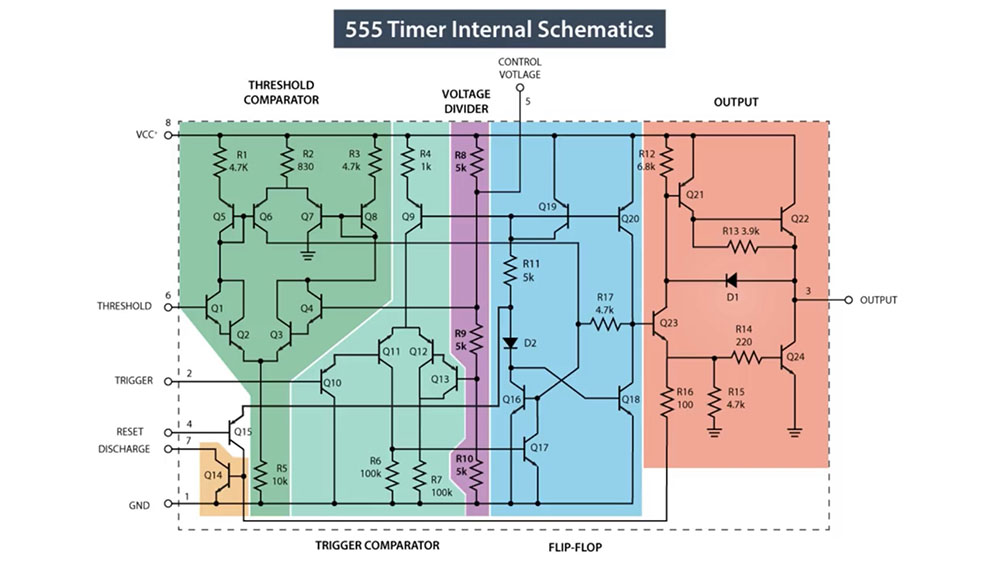

用不同颜色划分一下电路的功能区块。

包括:

1、Threshold Comparator(门限比较器,就是个电压比较器)

2、Trigger Comparator(触发比较器,就是个电压比较器)

3、Voltage Divider(分压电路)

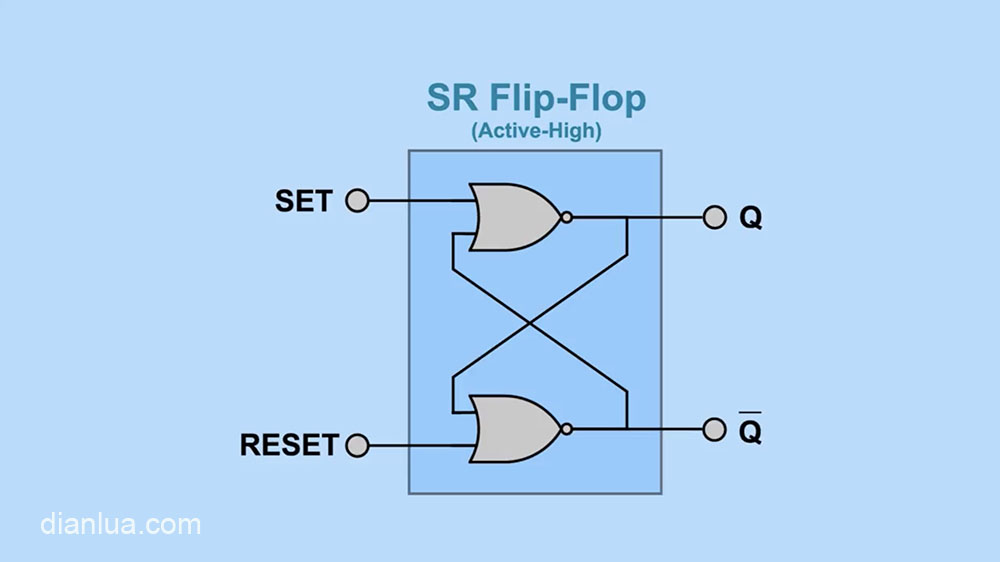

4、Flip-Flop(触发器,这里也叫RS触发器、复位/置位触发器、SR锁存器)

5、Output(输出电路)

6、Discharge(放电电路)

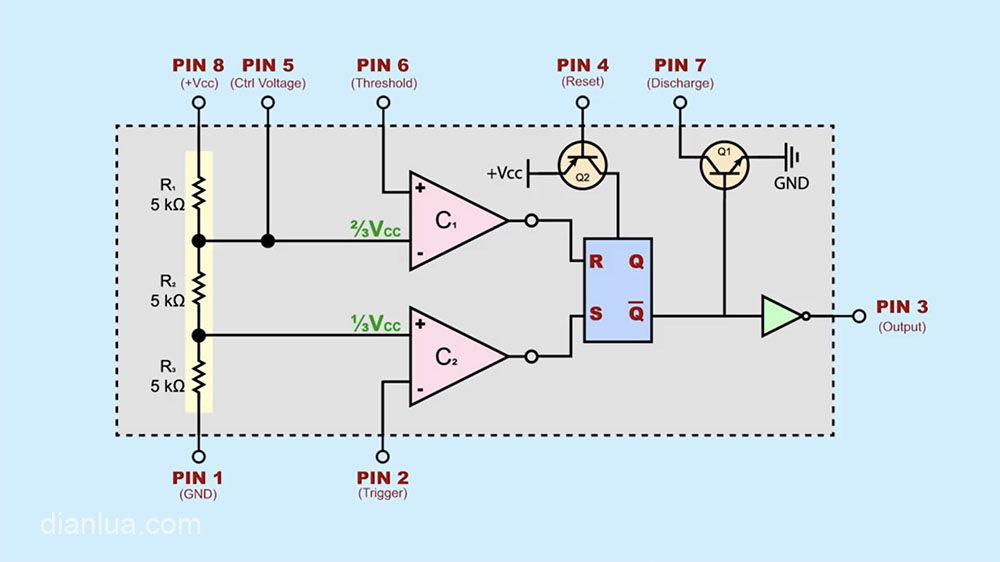

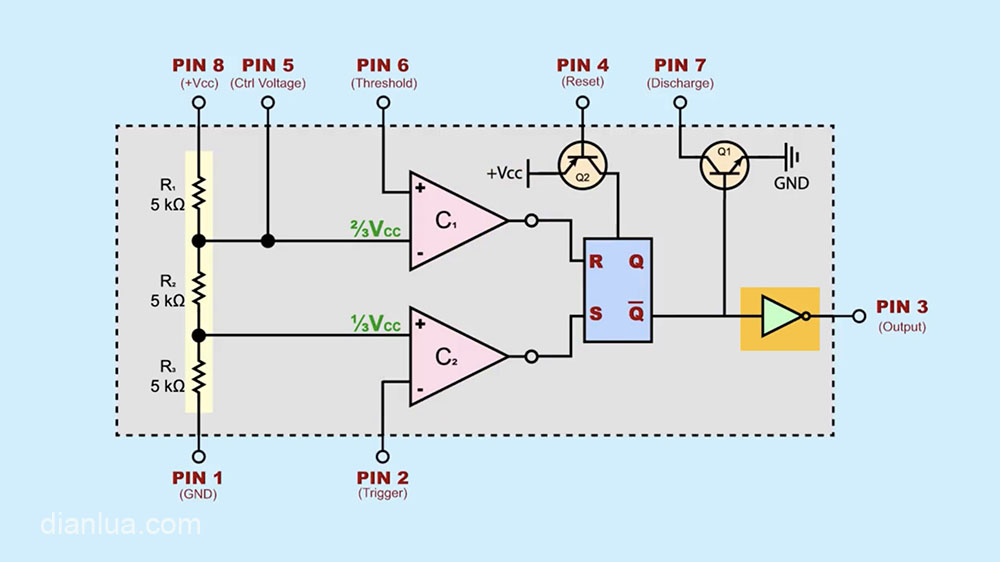

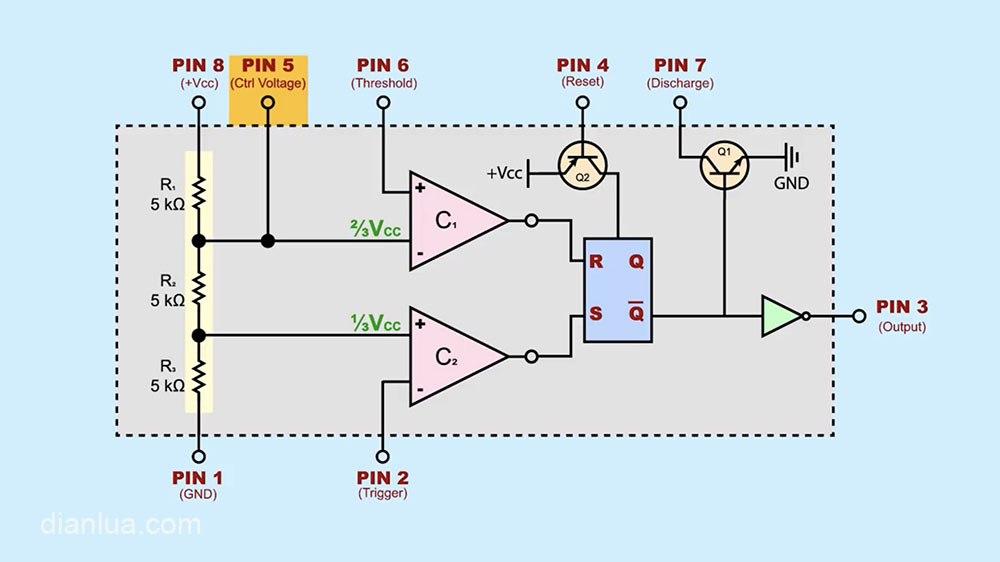

看起来有点复杂,等效简化为下图后就一目了然啦。

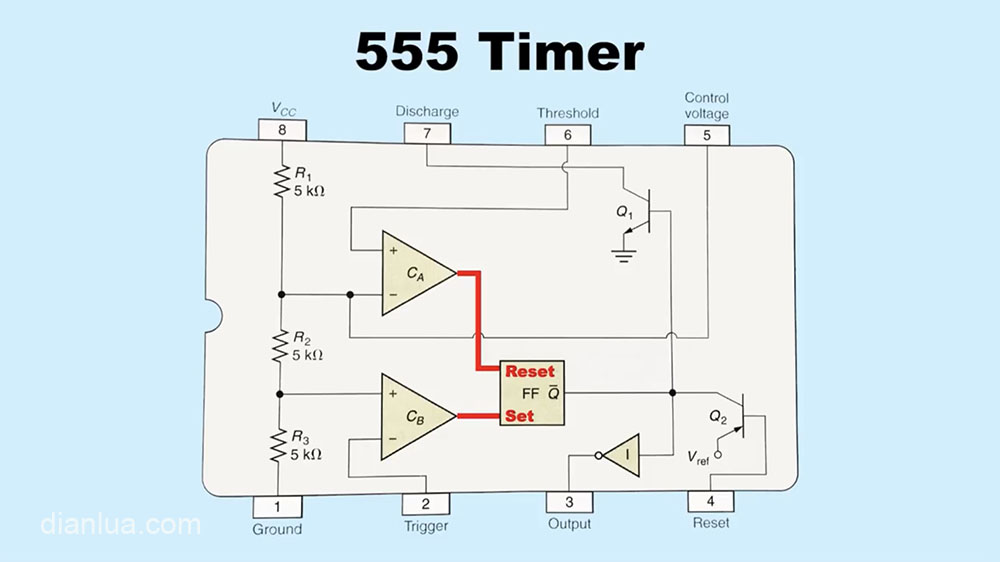

C1和C2就是两个电压比较器,即上文提到过的Threshold Comparator(门限比较器)和Trigger Comparator(触发比较器)。

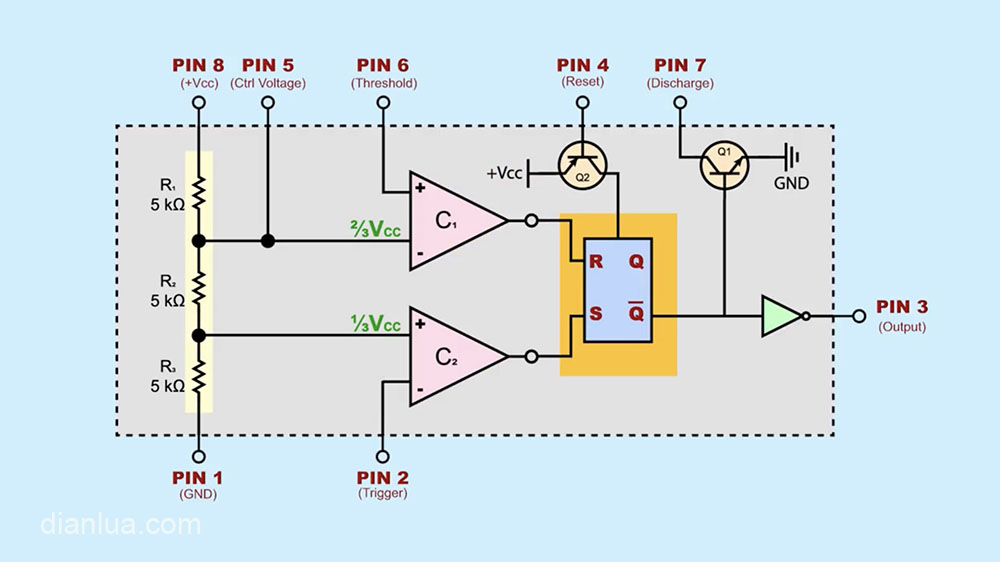

Flip-Flop(触发器),这里又叫RS触发器:

输出脚有个反相器。能将输入的低电平反相为高电平输出,同样能将输入的高电平反相为低电平输出。(高电平可以简单理解为电压接近电源电压Vcc,低电平可以简单理解为电压接近0)

Reset(复位)和Discharge(放电):

PIN4为输入引脚,为低电平时整个芯片处于复位状态,芯片不可用。

PIN7是放电引脚,用来给外部电路放电。

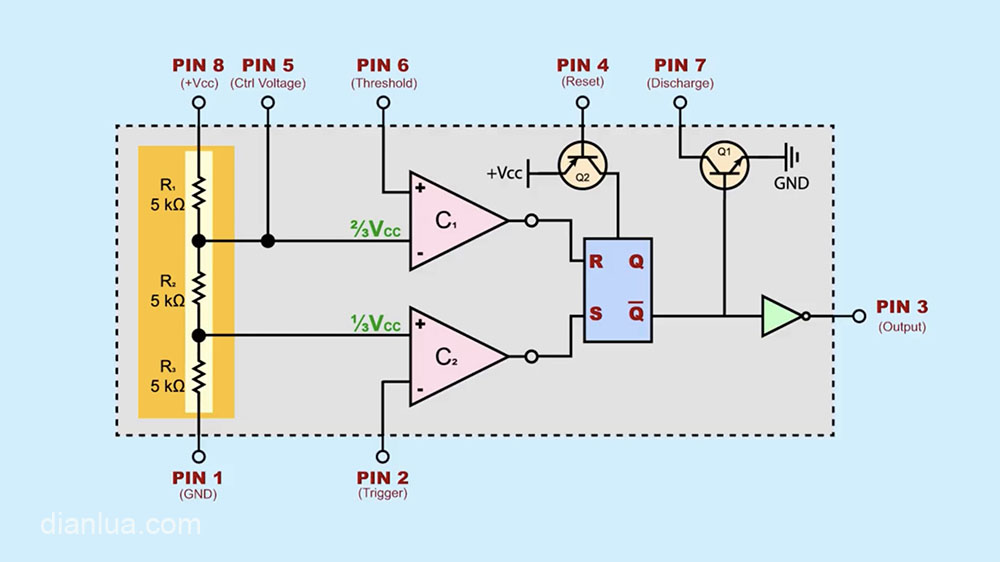

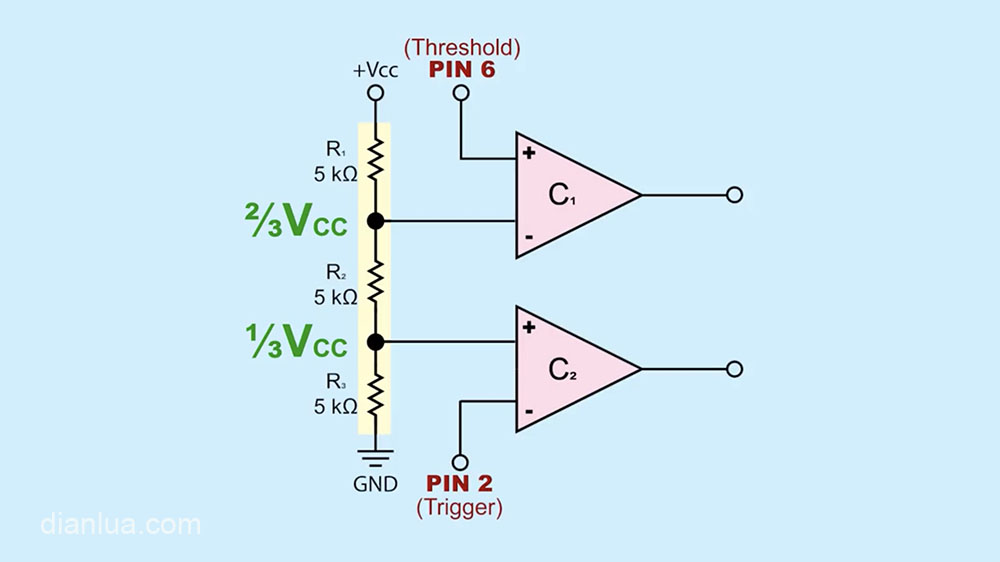

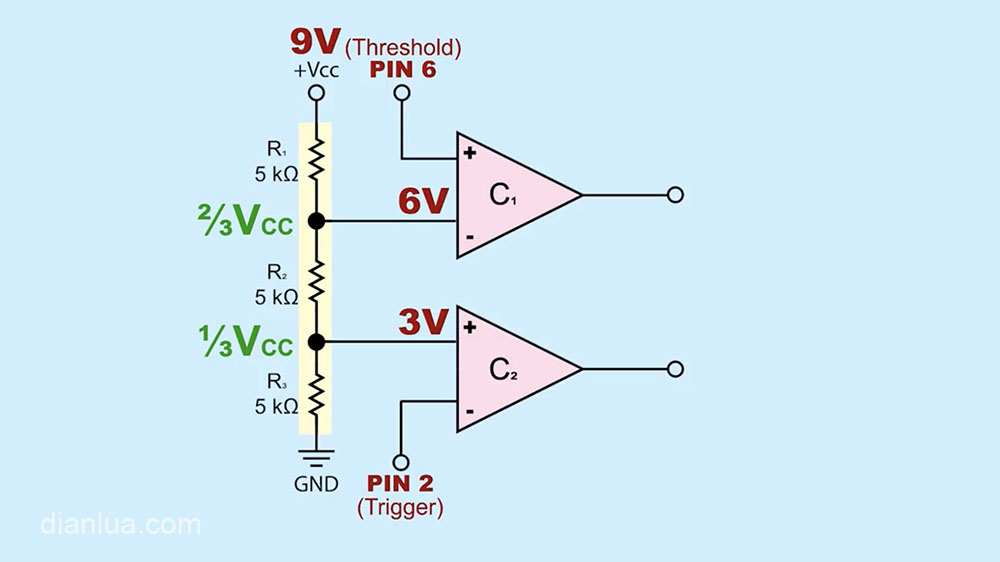

Voltage Divider(分压电路):

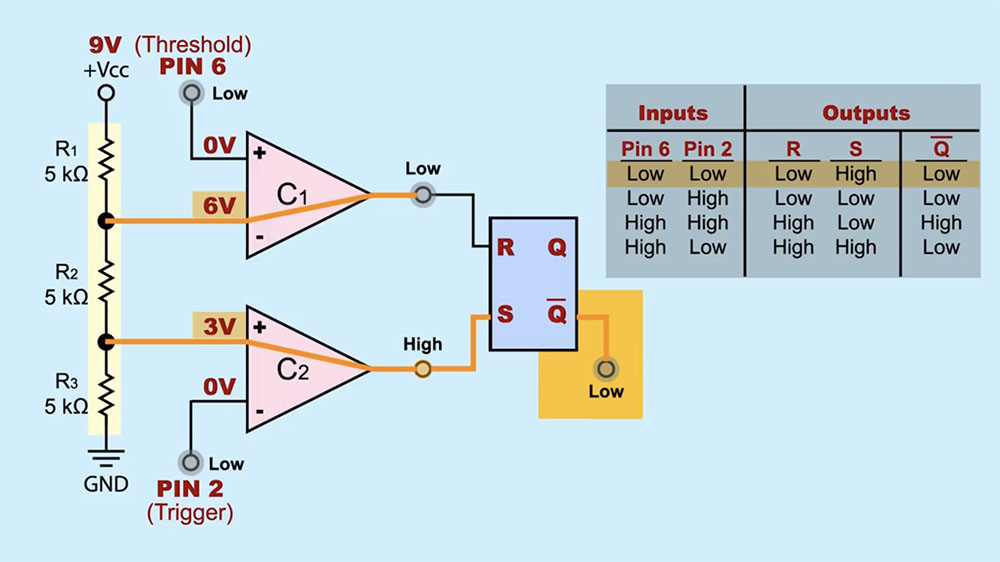

3个5kΩ电阻将Vcc电压三等分。

2/3Vcc输入到电压比较器C1的反向输入端。

1/3Vcc输入到电压比较器C2的正向输入端。

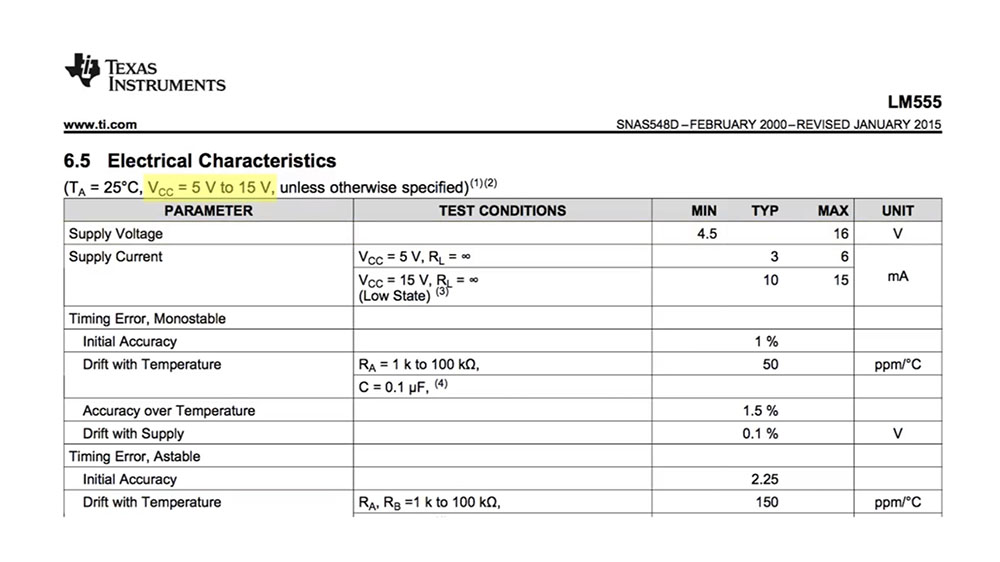

Vcc电压的范围,需要查看芯片的数据手册,这里的数据手册标示为5V到15V。

假设Vcc为9V时,2/3Vcc = 6V,1/3Vcc = 3V。

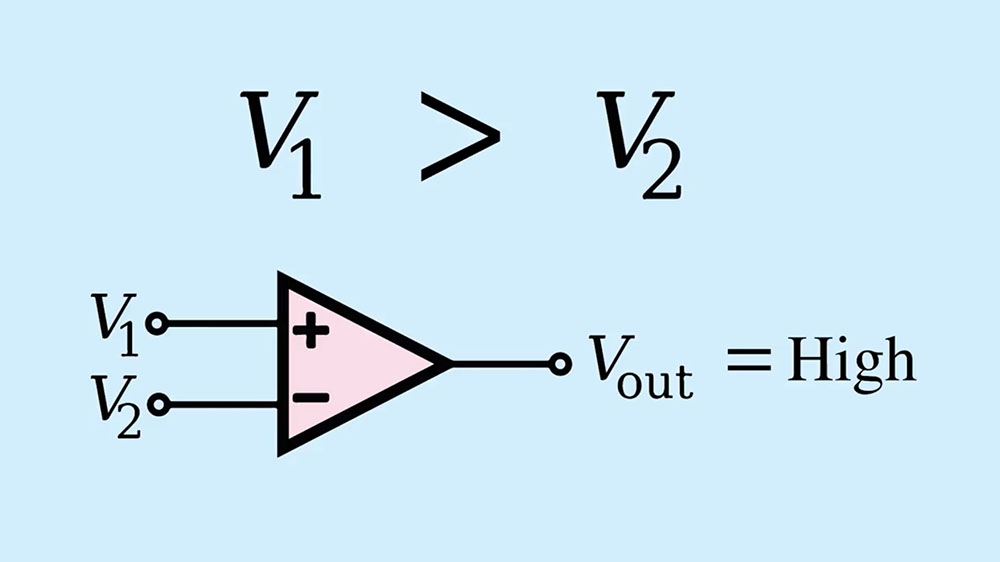

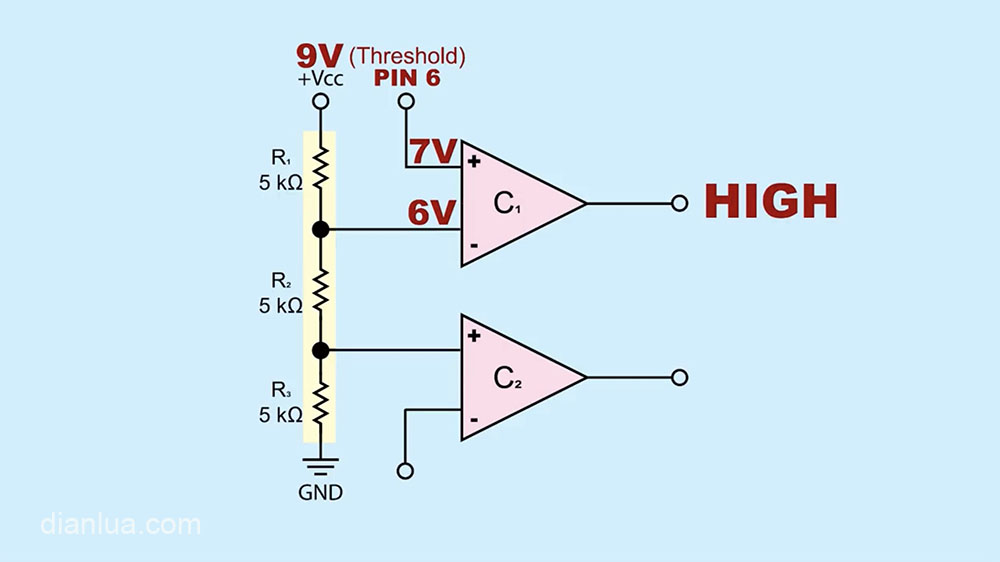

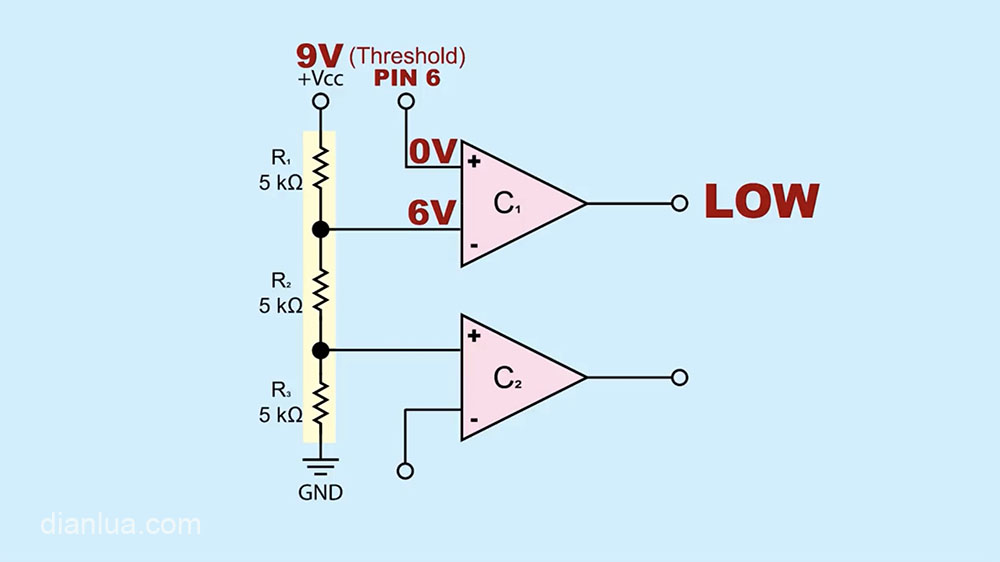

对于电压比较器来说,当"正向输入端的V1" > "反向输入端的V2”时,输出Vout = High高电平。

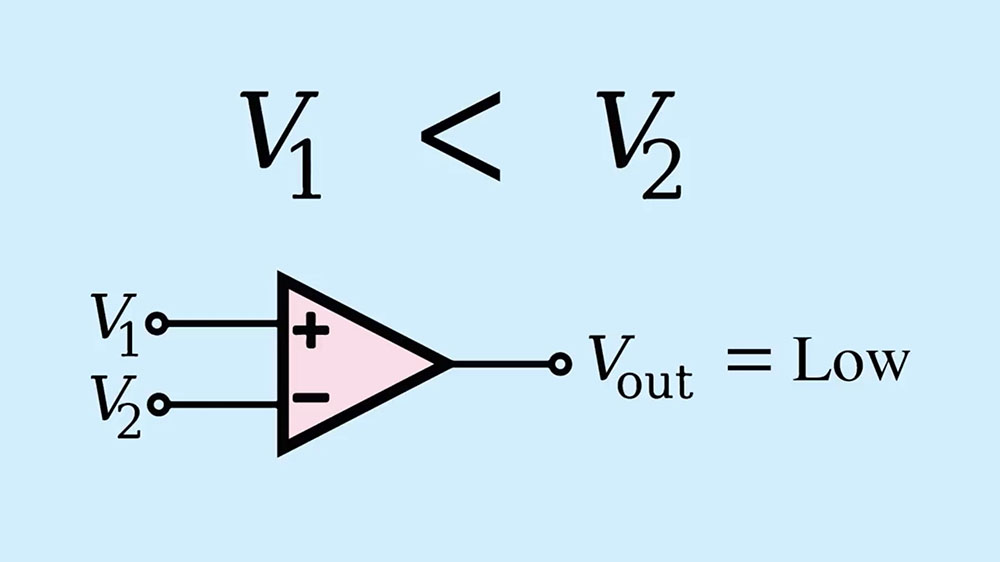

当"正向输入端的V1" < "反向输入端的V2”时,输出Vout = Low低电平。

所以当555定时器第6脚为7V时,电压比较器C1的"同相输入端(7V)" > "反向输入端(6V)",电压比较器C1输出HIGH高电平。

当555定时器第6脚为0V时,电压比较器C1的"同相输入端(0V)" < "反向输入端(6V)",电压比较器C1输出LOW低电平。

电压比较器C1、C2将电压比较的结果输出给RS触发器。

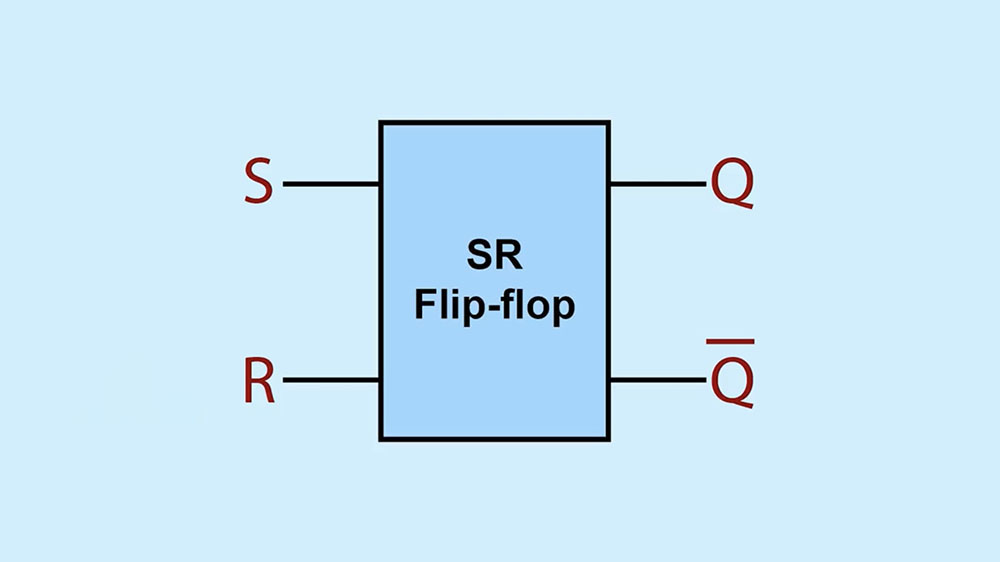

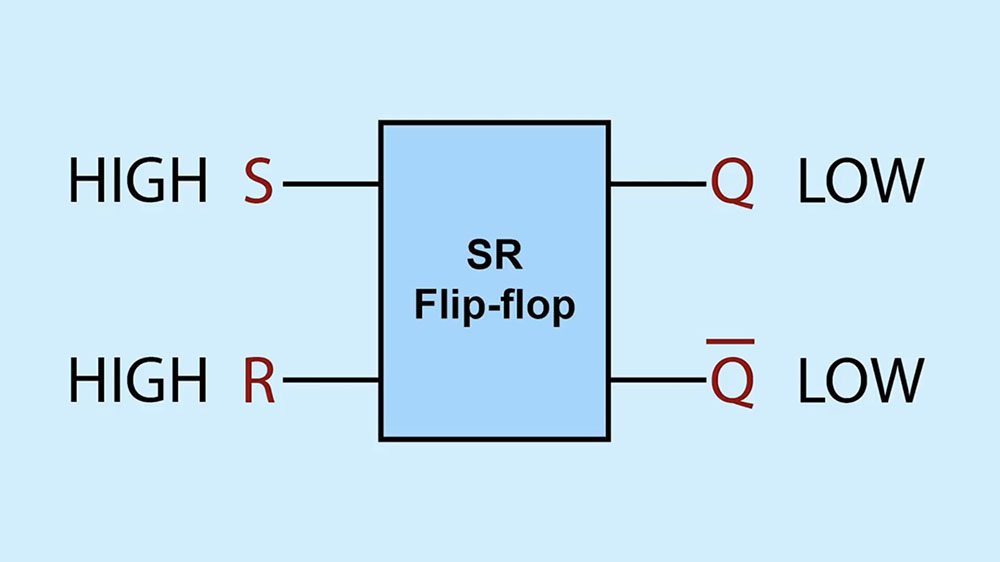

RS触发器有两个输入脚,分别为R和S:

R代表Reset(复位);

S代表Set(置位)。

RS触发器两个输出脚,分别为Q和非Q(“非Q”的符号是在Q的上面有一个横杠):Q和非Q的电平,在一般情况下互为相反,即Q为高电平,那么非Q为低电平。

其内部是由两个“或非门”组成。

在下面我们将看到在RS触发器定义里的三个特性。

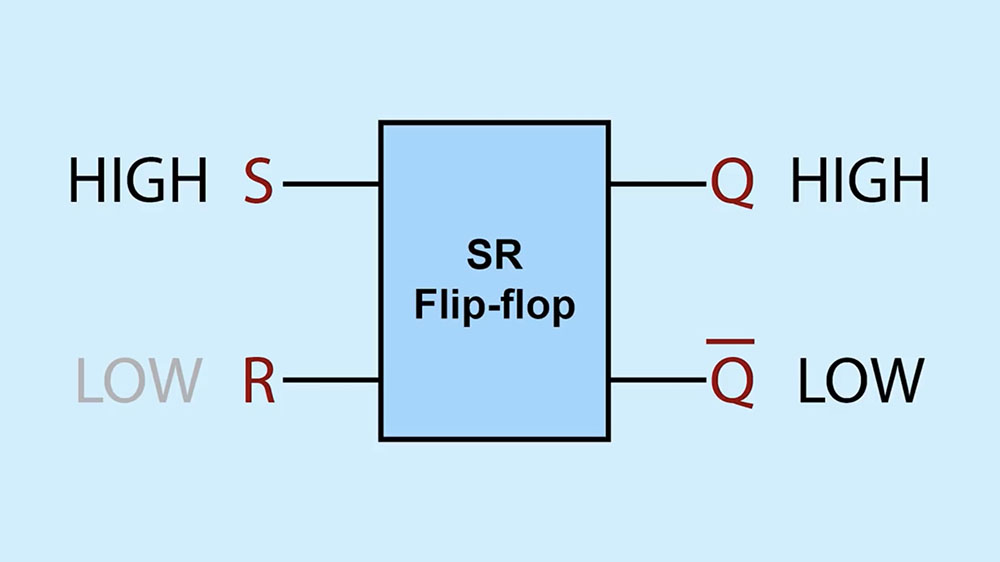

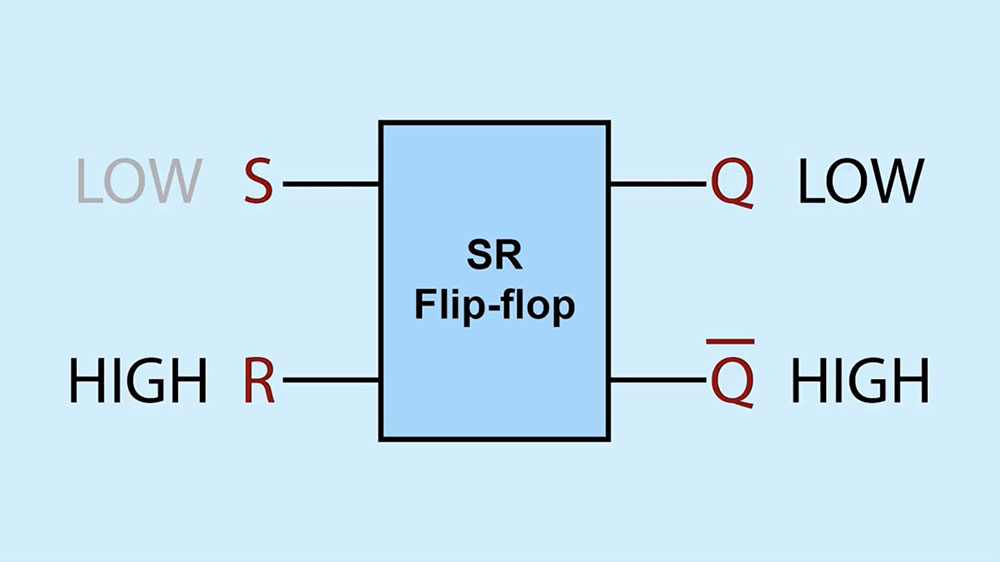

特性1:S、R为高电平有效。即S为高电平,就会把Q置位为1;R为高电平,就会把Q复位为0。

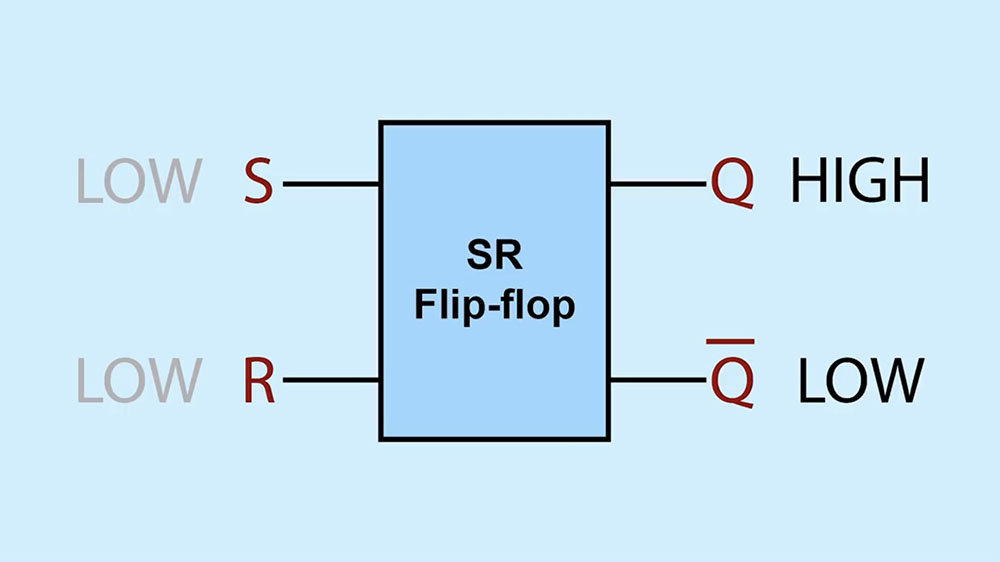

特性2:S、R同时为低电平时,Q和非Q将保持原来的状态不变。

特性3:S和R不能同时为高电平。这是RS触发器的定义规定的,但实际在555定时器的应用里,是可能出现其内部RS触发器的S和R同时为高电平的这种情况,稍后将展开讨论。

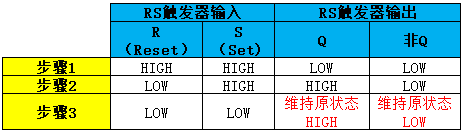

来看RS触发器的输入输出关系:

1、当S、R分别输入为HIGH、LOW时,Q被置位为HIGH,与之对应非Q为LOW。(特性1)

2、此时将S、R分别改为输入LOW、LOW时,Q、非Q将保持原来的状态,即仍为HIGH、LOW。(特性2)

3、当S、R分别输入为LOW、HIGH时,Q被复位为LOW,与之对应非Q为HIGH。(特性1)

4、此时将S、R分别改为输入LOW、LOW时,Q、非Q将保持原来的状态,即仍为LOW、HIGH。(特性2)

5、当S、R分别输入为HIGH、HIGH时,Q和非Q均为LOW。(见特性3,此为RS触发器定义里禁止出现的状态,可以看出此时Q和非Q的状态也不是相反的了,变成了相同的LOW)

为什么在RS触发器的定义里,要禁止出现这种状态呢?因为S、R同时为HIGH时,后续如果S、R是都变成LOW,那么由于S、R在都变成LOW的过程中,时间先后上总有细微的误差,S、R可能先变成LOW、HIGH,也可能先变成HIGH、LOW,这导致Q和非Q的状态不能确定。

当S比R先变成LOW时,最终Q和非Q分别为LOW、HIGH:

当R比S先变成LOW时,最终Q和非Q分别为HIGH、LOW:

所以在分析555定时器内部电路时,要谨记RS触发器的S、R为HIGH、HIGH时,避免下一步就变为LOW、LOW。

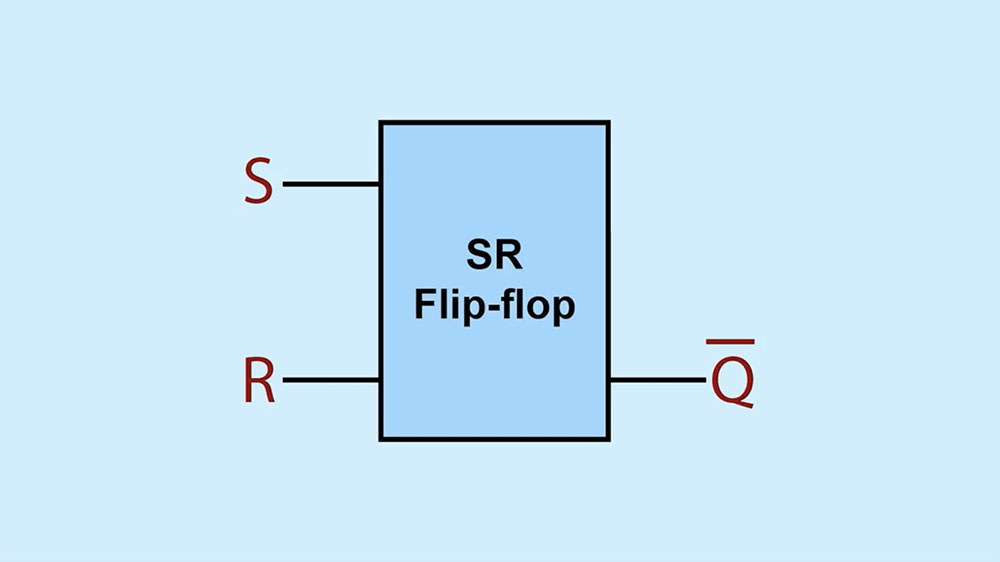

另外,由于555定时器里面只使用了非Q,没有使用Q,所以我们只看非Q就好了。

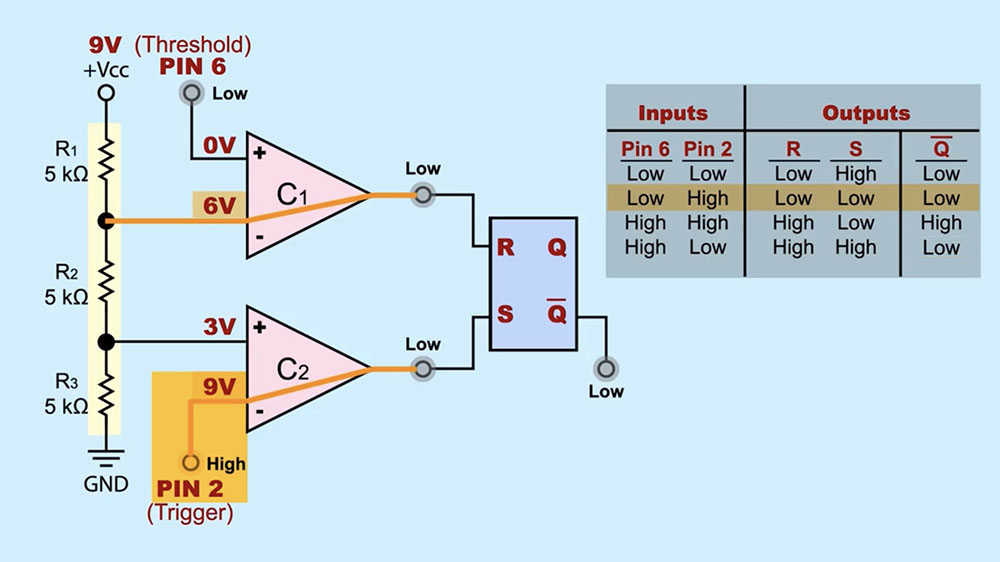

1、PIN6、PIN2分别输入0V、0V时:

①、电压比较器C1比较两个输入端的电压,最后输出Low到RS触发器的R端。

②、电压比较器C2比较两个输入端的电压,最后输出High到RS触发器的S端。

③、R、S分别为Low、High,RS触发器最终在非Q端输出Low。

2、PIN6、PIN2分别输入0V、9V时:

①、电压比较器C1比较两个输入端的电压,最后输出Low到RS触发器的R端。

②、电压比较器C2比较两个输入端的电压,最后输出Low到RS触发器的S端。

③、R、S分别为Low、Low,RS触发器最终在非Q端输出Low,即保持原来的状态。

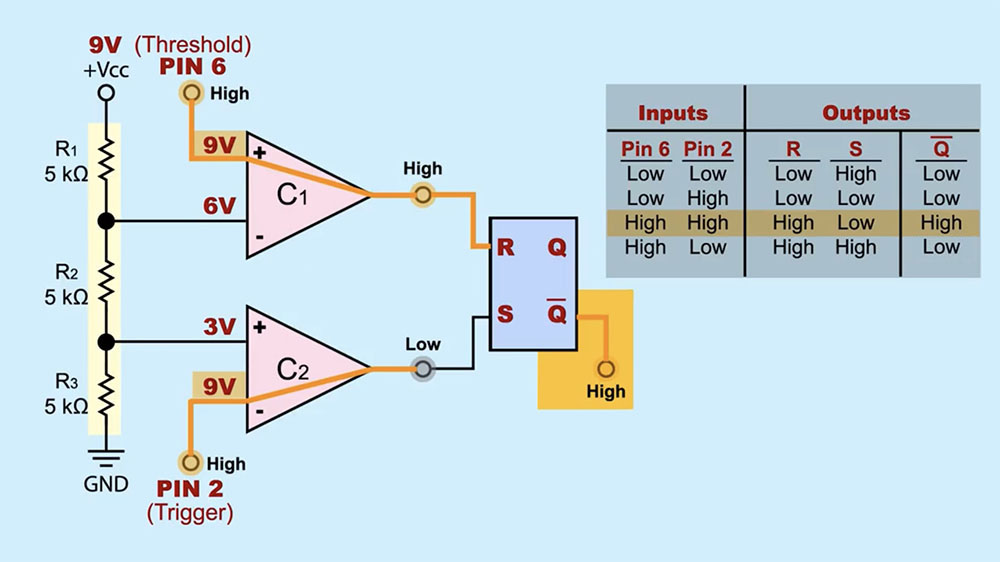

3、PIN6、PIN2分别输入9V、9V时:

①、电压比较器C1比较两个输入端的电压,最后输出High到RS触发器的R端。

②、电压比较器C2比较两个输入端的电压,最后输出Low到RS触发器的S端。

③、R、S分别为High、Low,RS触发器最终在非Q端输出High。

4、PIN6、PIN2分别输入9V、0V时:

①、电压比较器C1比较两个输入端的电压,最后输出High到RS触发器的R端。

②、电压比较器C2比较两个输入端的电压,最后输出High到RS触发器的S端。

③、R、S分别为High、High,RS触发器最终在非Q端输出Low。(如前所述,这里要注意避免R、S在下一步是变为LOW、LOW)

555定时器的PIN5是控制阈值电压脚。

PIN5接到电压比较器C1的反向输入端,可以让人直接控制电压比较器C1的阈值电压。

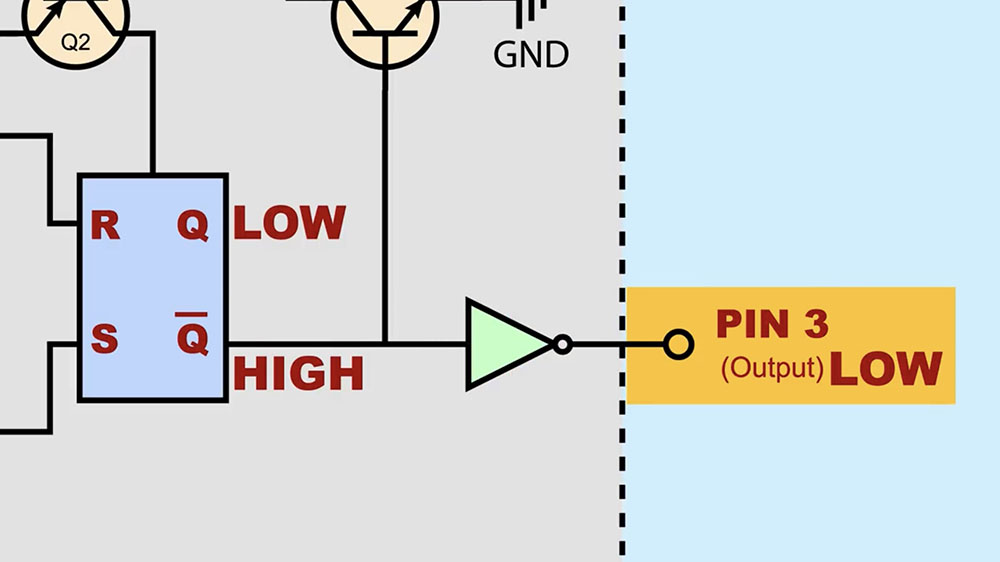

555定时器的PIN3是芯片的输出脚。

PIN3和RS触发器的非Q之间有1个反相器。

当非Q输出HIGH时,PIN3输出LOW,两者为反相关系。

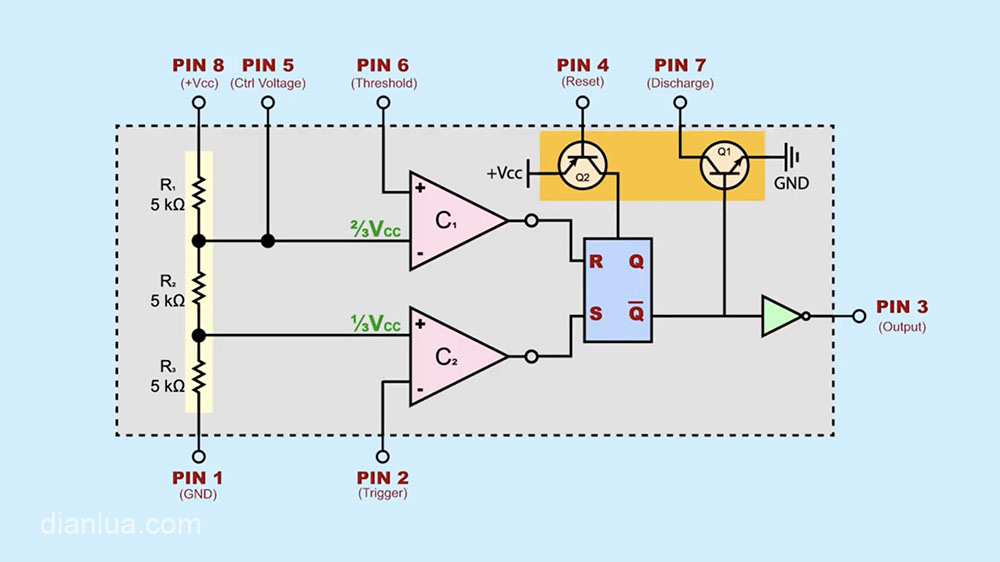

555定时器的PIN4是芯片的复位脚。当PIN4被接到低电平时,整个555定时器芯片被复位,PIN3将输出LOW。(图中三极管Q2的发射限流电阻未画出)

555定时器的PIN7是芯片的放电引脚。对外放电时,内部三极管Q1导通。(图中三极管Q1的基极限流电阻未画出)

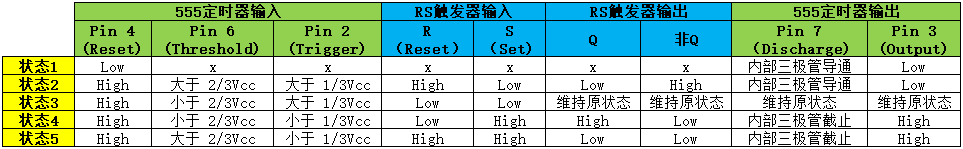

555定时器芯片的输入输出特性功能表总结如下,分为5种状态,后续在分析555定时器的应用电路时可借助该表进行分析:

注:在“状态5”时,下一步不能变成“状态3”,否则将导致输出结果不能确定。

至此,555定时器芯片内部电路的分析到此完毕,是不是感觉有点意犹未尽?

那是因为本文仅仅对芯片内部的电路做了分析,没有对芯片的应用电路做实例分析。所谓的空有内功心法,但是没有练过一招一式。

后续看到各种不同厂家生产的555定时器芯片所做成的应用电路时,可以参考本文讲解的芯片工作原理,多看多分析,积累越来越多的招式。

最后,关于电路的学习,希望大家,enjoy!(本文有点长,建议收藏,随时查阅。)

2023年6月5日 下午4:36 沙发

555真的是经典,大佬分析的很透彻